TPU論文の翻訳(2)

6. エネルギーの比例性

ハードウェアがフルパワーのときに、十分な電力と冷却を供給する必要があるため、TDP(熱設計電力)は供給電力のコストに影響する。ただし、この電力料金は、作業負荷が日中に変動するために消費される平均に基づいている。 [Bar07]は、サーバーが時間の10%未満で100%ビジーである時には、サーバーは、実行された作業量に比例した電力を消費する必要があるという比例性を発見したとしている。前章での消費された電力の見積もりは、Googlデータセンターで見られたTDPの割合に基づいている。

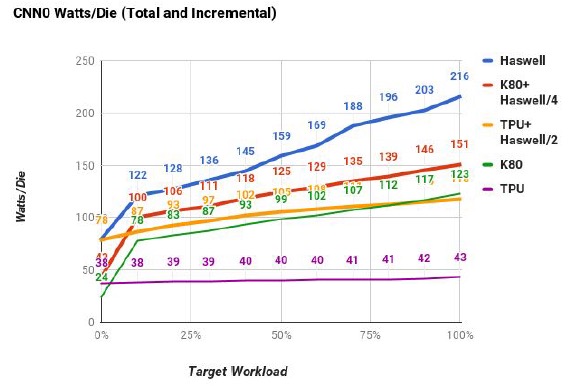

提供されたワークロード使用率が0%から100%まで変化し、ワークロードの10%デルタのバケットで収集された場合のパフォーマンスと電力を測定した[Lan09]。図10は、CNN0のワークロードを変化させることによって、3つのチップのサーバーあたりのダイの数をサーバーの数で割ったものである。 GPUとTPUの増分(K80とTPU)と合計電力(K80 + Haswell / 4とTPU + Haswell / 2)をプロットしている。すべてに同じバッチサイズが与えられていることに注意。

図10

図10.ターゲットプラットフォーム使用率が0%から100%まで変化する時のCNN0のワット/ダイ。 Total GPUとTPUのパワーは赤とオレンジのラインで、Incrementalパワーは緑と紫のライン。サーバは2CPU、8GPUまたは4TPUを持っているので、それぞれ2,8、および4で割って正規化している。TPUはダイ全体で最低118W(TPU + Haswell / 2)、ダイごとに40W(図10ではTPU)だが、エネルギーの比例性は低い。10%の負荷でTPUは、100%負荷の時の88%の電力を使っている。 (短い設計スケジュールにより、多くの省エネ機能が組み込まれていなかった。)

当然のことながら、Haswellはグループの比例比で最高である。10%の負荷の場合、100%負荷の56%の電力を使用する。 K80はTPUよりもCPUに近く、10%の負荷で全負荷電力の66%を使用する。計算上の境界ではないLSTM1も同様に動作する.10%の負荷では、CPUはフルパワーの47%を使用し、GPUは78%を使用し、TPUは94%を使用する。

アクセラレータのホストになる場合、CNN0を実行すると、サーバーの電力使用量はどうなるだろうか? GPUとTPUの負荷が100%の場合、CPUサーバーはGPUのフルパワーの52%、TPUのフルパワーの69%を使用する。したがって、Haswellサーバーと4台のTPUは、20%未満の追加電力を使用するが、CNN0はHaswellサーバー単独の80倍の速度で動作する(4台のTPU対2つのCPU)。

7. もう一つのTPUのデザインの評価

FPUのように、TPUコプロセッサは比較的簡単に評価できるマイクロアーキテクチャを備えているため、6つのアプリケーションのパフォーマンスモデルを作成した。

表7に、モデル結果とハードウェアパフォーマンスカウンタの違いを示す(平均値は10%未満)。次に、メモリ帯域幅、アキュムレータのクロックレートと数、行列の乗算単位サイズを変えてパフォーマンスをモデル化した。

表7

表7. TPUハードウェア・パフォーマンス・カウンターとTPUパフォーマンス・モデルの間のクロック・サイクルの相違。平均は8%。

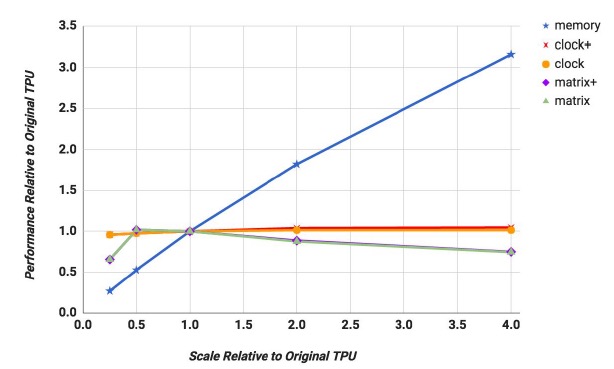

図11は、0.25x〜4xの範囲でこれらのパラメータをスケールする時、TPUダイの平均性能がどう変わるかを示す。加重平均をプロットしているが、幾何学的平均に似ている。クロックレートを上昇させるだけの影響(図11のclock)を評価することに加えて、クロックレートが増加するとコンパイラーが、ただちにより多くのメモリー参照を維持できるようにして、アキュムレータの数が対応してスケーリングされる設計(clock+)をプロットする。 同様に、1次元の立ち上がりの2乗(matrix+)でアキュムレータの数を増やした場合の、行列ユニットの拡張をプロットする。行列の乗数が両方の次元で増加するだけでなく、行列ユニットを増加させるからである。

図11

図11. 行列のスケールが、0.25xから4xに変わった時のTPUのパフォーマンスの加重平均。メモリ帯域幅、クロックレート+アキュムレータ、クロックレート、行列ユニットの次元+アキュムレータ、および行列ユニットの次元の加重平均。加重平均は個々のDNNの寄与を見るのが難しくなるのだがが、MLPとLSTMは4Xメモリ帯域幅で性能が3倍に向上するが、より高いクロックからは何も得られていない。 CNNの場合は逆で、 4Xクロックでは2倍になるが、より高速なメモリのメリットはほとんどない。より大きい行列乗算ユニットはDNNを助けることはない。

第一に、メモリ帯域幅(メモリ)を増やすことが最も大きな影響を与える。メモリが4倍になると、パフォーマンスは平均で3倍向上する。

第二に、クロックレートは、アキュムレータの有無にかかわらず平均でほとんど利益を持たない。理由は、MLPとLSTMはメモリにバインドされているが、CNNだけが計算にバインドされているためでである。6つのDNNすべての加重平均値しか示していないため、図11では分かりにくいが、クロックレートを4倍にするとMLPおよびLSTMにほとんど影響はなく、CNNのパフォーマンスは約2倍向上する。

第三に、図11の平均パフォーマンスは、アキュムレータが増えたかどうかにかかわらず、すべてのアプリで行列ユニットが256x256から512x512に拡大すると若干低下する。この問題は、大規模ページの内部のフラグメンテーションの問題に似ているが、それは2次元であるために悪化するだけである。 LSTM1で使用される600x600行列を考えてみよう。 256x256のマトリックスユニットでは、タイル600x600まで9ステップ、合計18 usの時間がかかる。より大きい512x512ユニットでは4ステップしか必要なくなるが、各ステップは32 us で4倍長くなる。我々のCISC命令は長いので、デコードは重要ではなく、DRAMからロードするオーバーヘッドを隠すことはない。

表8

表8. NNアプリケーションごとに使用される24 MiB ユニファイド・バッファーの最大MiB。これらのアプリには14 MiB Unified Bufferで十分である。

次に、性能モデルを使用して、もし、我々がさらに15カ月の時間があって、同じプロセス技術で設計すると仮定して、仮想的なTPUダイ(TPU ')を評価した。

より積極的な論理合成とブロック設計により、クロック速度が50%向上した。 K80のようにGDDR5メモリ用のインタフェース回路を設計すると、ウェイトメモリの帯域幅が5倍以上に向上し、ルーフラインの分水嶺が1350から250に変わった。

図11に示すように、クロックレートを1050MHzに上げてみたが、メモリーの性能はほとんど変化しない。クロックを700MHzにして、GDDR5を、ウェイト・メモリーに使用した場合、幾何平均の増加は印象的な2.6に、加重平均は3.9に飛躍的に向上した。ただ、その両方を行ってみたが、幾何平均値(2.9)は上がるが、加重平均値は上がらないため、TPUはより速いメモリを持っているだけだということになる。

図11には、ホストサーバーの時間は含まれていない。表5を使用して、TPUに対するホストサーバーの対話オーバーヘッドの時間を計算した。同じ余分な時間を追加すると、TPU 'は2.6から1.9、3.9から3.2になる。この変更には、アプリのシェアを実行するCPU時間は含まれていないので楽観的な評価である。悲観的なのは、TPUを3倍高速化した場合、ホストコードを、積極的に調整しなければならない可能性が高いということである。

DDR3のウェイト・メモリだけを同等のGDDR5メモリに置き換えるだけでも、メモリのチャネル数を4倍にする必要がある。この改善のために、ダイサイズは、約10%拡大する。ただし、メモリ帯域幅が大きいほどユニファイド・バッファへの負荷が軽減されるので、ユニファイド・バッファを14 MiBに減らすと、面積の10%を戻すことができる。 1台のサーバに4台のTPUがあるので、GDDR5はまた、TPUシステムの電力予算を861ワットから約900ワットに増加させる。

図9

図9は、TPUの相対的な総合性能/ワット/ダイが、Haswellより31倍〜86倍、K80より25倍〜41倍飛躍することを示している。インクリメンタル・メトリックは、Haswellに比べて69倍〜196倍、K80に対して42倍〜68倍になる。

8. 議論

この章では、[Hen18]のスタイルに従って、「誤謬」と「落とし穴」を、論駁する。

誤謬:データセンターのNN推論アプリケーションは、応答時間と同じくらいスループットを重視する。

2014年に、TPUのピーク性能に達成する為に、バッチサイズに十分な大きさを持たせるか、待ち時間要件はそんなに厳しくない方がいいと提案され、逆に、Googleの開発者は、自分たちが応答時間の要求が強いことに驚いた。 動いていたアプリケーションの一つは、オフラインの画像処理であり、インタラクティブなサービスにするにしても、直感的に言えば、TPUが必要な場合は、大部分が大量のバッチを蓄積するだろうというものだった。応答時間に関心を持つ2014年のあるアプリケーションの開発者(LSTM1)でも、2014年には、応答時間は10ミリ秒が限界だと語っていたのだが、実際にTPUに移植すると7ミリ秒に短縮された。

TPUに対する、このような多くのサービスからの予期せぬ欲求と、低応答時間への志向の影響との兼ね合いから、方程式が変わった。アプリケーションの作者は、より大きなバッチが蓄積されるのを待たずに、待機時間を短縮することを選択した。幸運なことに、TPUには、対話型サービスの応答時間の目標を達成するための、シンプルで繰り返しが可能な実行モデルがあり、小さなバッチサイズであっても、現代のCPUやGPUよりも高いパフォーマンスをもたらす、高いピークスループットがある。

誤謬:K80 GPUアーキテクチャはNNの推論によくマッチしている。

GPUは、伝統的には、高帯域幅のDRAMと数千のスレッドに依存した高スループットのアーキテクチャと見なされてきた。この視点は、K80がHaswellよりも推論で少しだけ早く、TPUよりもはるかに遅い理由を説明するのに役立つ。 K80の後継機には、確かにピーク推論のパフォーマンスを向上させるための最適化が含まれているが、スループット指向のアーキテクチャ上のアプローチを考えれば、GPUが厳しいレイテンシの制限を満たすのは難しいだろう。第7章で示したように、TPUを改善する余地は十分にあるため、それは簡単な目標ではないのだが。

落とし穴:システム設計者は、重要なNNタスクを無視している。

ISCA 2016の論文の15%が、 [Alb16] [Che16a] [Ch16] [Han16] [Kim16] [LiK16] [Liu16]のNNのハードウェアアクセラレータを取り上げているように、システム設計者のコミュニティがNNに注意を払っていることを嬉しいことだ。 [Rea16] [Sha16]!ただ、悲しいかな、この9件の論文はすべてがCNNについてのもので、他のNNについては、2件しか触れられていなかった。

CNNはMLPよりも複雑で、NNの競争では、とてもよく目立つ[Rus15]ことは、そのの魅力を説明するかもしれないが、それは、GoogleデータセンターのNNワークロードの約5%にすぎない。エッジデバイスではCNNが一般的なのだが、CNNモデルのボリュームは、データセンター内のMLPやLSTMにはまだ追いついていない。我々は、システム設計者がMLPやLSTMを少なくともぎりぎりまで加速させることを願っている。

落とし穴:NNハードウェアの場合、Inferences Per Second(IPS)は、パフォーマンスを計る指標としては不正確である。

我々の結果は、IPSは、NNハードウェアの全体的なパフォーマンスのサマリーとしては貧弱であることを示している。なぜなら、それは、アプリケーションの典型的な推論の複雑さ(例えば、NN層の数、サイズ、タイプ)を反映していないからである。

たとえば、TPUは360,000 IPSで4層MLP1を稼動させるが、89層CNN1は4,700 IPSで稼働するため、TPU のIPSは75倍にもなる!したがって、IPSを単一スピードのサマリーとして使用すると、NNアクセラレータでは、通常のプロセッサでのMIPSやFLOPSは[Hen18]よりも誤解を招くことになるので、IPSはもっと軽視されていい。

NNマシンをよりよく比較するには、幅広いNNアーキテクチャに移植するための高水準のベンチマークスイートが必要となる。 Fathomはこのようなベンチマークスイート[Ado16]で有望な新しい試みである。

誤謬:Boostモードが有効になっていれば、K80 GPUの結果がはるかに良くなる。

K80ブースト・モードがTCOに及ぼす悪影響を除いて(第3章)、LSTM1で測定た。ブースト・モードでは、クロックレートが560MHzから875MHzに1.6倍増加し、パフォーマンスは1.4倍上がったが、電力は1.3倍になる。パフォーマンス/ワットの純利益は1.1倍であるため、LSTM1の場合、ブーストモードはGoogleのエネルギー速度分析に、軽い影響しか与えない。

誤謬:CPUとGPUの結果は、それらをより効率的に使用し、新しいバージョンと比較すると、TPUに匹敵する。

当初は、AVX2整数サポートを効率的に使用するために重要な作業が行われていたため、CPU上のDNNが1つの場合には8ビットの結果しか得られなかった。利益は約3.5倍だった。 1つの例外を除いて、すべてのCPUでの結果を浮動小数点で表示するのは、それ自身のルーフラインを使用した方が紛らわしいことではない。

すべてのDNNのスピードアップが同じ場合、パフォーマンス/ワット率は41〜83倍から12〜24倍に低下する。新しい16nm、1.5GHz、250W P40データセンターGPUは47Teraの8ビットのops /秒を実行できるが、2015年の初めには利用できなかったため、3つのプラットフォームは、最新のものではない。

我々は、また、我々の厳しい時間の制限の中で、発表されたP40ピークの割合を知ることもできなかった。7章は、新しいチップで比較した場合、K80のGDDR5メモリを使用するだけで、28nm、0.7GHz、40WのTPUのパフォーマンスを3倍にすることができることを示している(さらに10Wのコストで)。

落とし穴:パフォーマンス・カウンタは、NNハードウェアに、後からの補足として追加された。

TPUには106個のパフォーマンスカウンタがあるが、必要な場合はもう少し欲しい(表3参照)。 NNアクセラレータの存在理由はパフォーマンスである。何が起きているかについての良い直感を得るには、我々は、まだ、進化の早い段階にいる。

誤謬:2年間ソフトウェアを調整したが、TPUのパフォーマンスを向上させる唯一の道は、ハードウェアのアップグレードである。

TPU上のCNN1のパフォーマンスは、開発者とコンパイラ作成者がCNN1とTPUハードウェアを一致させるためにより多くの努力を払っていれば改善する可能性がある。

例えば、開発者はアプリケーションを再編成して、4つのフル・コネクト層に対してコンボリューション層から複数の短いバッチを1つのより深いバッチ(32〜128)に集約できる。そのような単一の層は、マトリックス単位の利用を改善するであろう(表3)。 CNN1は現在TPU上でCPUより70倍以上高速に動作しているため、CNN1の開発者は既に非常に満足しているため、このような最適化が実行されるかどうかは不明なのだが。

9. 関連する仕事

2つの調査論文を見ると、カスタムNN ASICが少なくとも25年前にさかのぼると述べられている。[Ien96] [Asa02]。

例えば、CNAPSチップは16ビット×8ビットの64 SIMDアレイを含み、複数のCNAPSチップをシーケンサー[Ham90]に一緒に接続することができた。

Synapse-1システムは、一度に16の16ビットの乗算を実行するMA-16と呼ばれるカスタムのシストリック多重積算チップに基づいていた[Ram91]。システムはいくつかのMA-16チップを連結し、活性化機能を実行するカスタムハードウェアを持っていた。

T0カスタムASICによって加速された25のSPERT-IIワークステーションは、NNトレーニングと音声認識の推論の両方を行うために1995年から展開された[Asa98]。 40-MHz T0は、ベクトル命令をMIPS命令セットアーキテクチャに追加した。 8レーン・ベクトル・ユニットは、8ビットおよび16ビット入力に基づいてクロック・サイクルごとに最大16個の32ビット算術演算結果を生成できるため、SPARC-20ワークステーションよりも推論で25倍、トレーニング時で20倍高速だった。彼らは、トレーニングには16ビットではが不足しだということを見つけ、代わりに2つの16ビットワードを使用してトレーニング時間を2倍にした。その欠点を克服するために、ウェイトの更新にかかる時間を短縮するために、32〜1000個のデータセットの「束」(バッチ)を導入した。

より最近のDianNaoファミリのNNアーキテクチャは、NNアプリケーションに現れるメモリアクセスパターンを効率的にアーキテクチャでサポートすることで、チップと外部DRAMの両方でメモリアクセスを最小限に抑えた[Keu16][Che16a]。すべてが16ビット整数演算を使用し、すべての設計がレイアウトされたが、チップは作成されなかった。元のDianNaoは、44 KBのオンチップメモリを備えた64個の16ビット整数積和積算ユニットのアレイを使用し、1 GHzで動作し、0.5W [Che14a]を消費すると評価された。面積は、3mm2(65nm) 。この大半のエネルギーはDRAMのアクセスに使用されていたため、DaDianNaoの後継の1台(「大型コンピュータ」)には36 MiBの重みをチップに保持するeDRAMが含まれている[Che14b]。目標は、外部DRAMへのアクセスを避けるために、マルチチップシステムに十分なメモリを確保することだった。

後継のPuDianNao( "general computer")は、サポートベクトルマシン[Liu15]のような、DNN以外の伝統的な機械学習アルゴリズムを対象としている。また、CNNを対象としたShiDianNao(ビジョン・コンピュータ)もある。Dian15はアクセラレータをセンサに直接接続することでDRAMへのアクセスを避けた[Du15]。

Convolution Engineは、画像処理のためのCNNにも焦点を当てている[Qad13]。この設計では、64個の10ビット乗算累算器ユニットが導入され、45 nmで800 MHzで動作すると推定されるTensilicaプロセッサがカスタマイズされている。これは、SIMDプロセッサよりも8倍から15倍もエネルギー効率が高く、特定のカーネルだけのために設計されたカスタムハードウェアの2倍から3倍になると予測されている。

Fathomのベンチマーク・ペーパーは、GPUの実行推論がCPU [Ado16]よりもはるかに高速で、私たちと矛盾する結果を示しているようである。しかし、CPUとGPUはサーバクラスではなく、CPUには4つのコアしかなく、アプリケーションはCPUのAVX命令を使用せず、応答時間のカットオフもない(表4参照)[Bro16]。

Catapultは、[Far09] [Cha10] [Far11] [Pee13] [Cav15] [Zha15]を提案したDNNをサポートするために再構成可能性を使用する最も広く展開された例である。彼らは、GPU上でFPGAを選択して、電力を削減するだけでなく、レイテンシに敏感なアプリケーションがGPUにうまく対応しないというリスクを削減した。 FPGAは、検索、圧縮、ネットワークインタフェースカードなどのために再利用することもできる[Put15]。

TPUプロジェクトは実際にはFPGAから始まったが、その時のFPGAがその時期のGPUと比較して性能競争力がないことを見て、放棄した。TPUはGPUよりもはるかに低電力であり、 FPGAとGPUの両方以上に大きなメリットをもたらす可能性がある。

Catapultは、2014年に最初に公開されたが(Putte)、2015年にTPUと並行して28nmのStratix V FPGAをデータセンターに導入して以来、200MHzクロック、3,926個の18ビットMAC、5 MiBのチップメモリ、11 GB /秒のメモリ帯域幅を持ち、25ワットを使用する。 TPUは、700MHzクロック、65,536個の8ビットMAC、28Mバイト、34GB /秒を有し、典型的には40ワットを使用する。Catapultの改訂版では、より新しいFPGAが使用され、2016年にはより大規模に展開された[Cau 16]。

Catapultは、2014年に最初に公開されたが(Putte)、2015年にTPUと並行して28nmのStratix V FPGAをデータセンターに導入して以来、200MHzクロック、3,926個の18ビットMAC、5 MiBのチップメモリ、11 GB /秒のメモリ帯域幅を持ち、25ワットを使用する。 TPUは、700MHzクロック、65,536個の8ビットMAC、28Mバイト、34GB /秒を有し、典型的には40ワットを使用する。Catapultの改訂版では、より新しいFPGAが使用され、2016年にはより大規模に展開された[Cau 16]。

Catapult V1は、2.1GHz、16コア、デュアルソケットサーバ[Ovt15a]と同じくらい速く、シストリック行列乗算器を使用して、2.3倍でCNNを実行する。

Catapult V2の次世代FPGA(14nm Arria 10)を使用すると、パフォーマンスは最大7倍、さらには17倍になる可能性がある[Ovt15b]。これはリンゴとオレンジ程度の違いだが、現在のTPUのダイは、CNNを40倍から70倍まで高速化している(表2と6)。

おそらく最も大きな違いは、最高レベルのパフォーマンスを得るには、ユーザーが低水準のハードウェア設計言語Verilog [Met16] [Put16]と、高レベルのTensorFlowフレームワークを使用した短いプログラムを書く必要があることである。すなわち、再プログラム可能性は、FPGAのファームウェアからではなく、むしろ、TPUのソフトウェアから発生する。

TPUの導入後に登場した最近の研究は、重みとデータが非常に小さいかゼロの場合を最適化することによってDNNを加速する。私たちのタイトなスケジュールがTPUでのそのような最適化を妨げたのだが、我々の研究でも同じ可能性を見つけている。効率的な推論エンジンは、非常に小さな値をフィルタリングすることによって重み付けの数を約1/10 [Han15]だけ減らした最初のパスに基づいており、ハフマン符号化を使用して推論性能をさらに向上させる[Han16]。

TPUの導入後に登場した最近の研究は、重みとデータが非常に小さいかゼロの場合を最適化することによってDNNを加速する。私たちのタイトなスケジュールがTPUでのそのような最適化を妨げたのだが、我々の研究でも同じ可能性を見つけている。効率的な推論エンジンは、非常に小さな値をフィルタリングすることによって重み付けの数を約1/10 [Han15]だけ減らした最初のパスに基づいており、ハフマン符号化を使用して推論性能をさらに向上させる[Han16]。

Cnvlutin [Alb16]は、活性化の入力がゼロであるときの乗算を回避する。これは、おそらく部分的に負の値をゼロに変換するReLU非線形関数に起因する44%の時間であり、平均1.4倍のパフォーマンス向上につながる。

Eyerissは、入力がゼロのときの計算を避けることで、メモリのフットプリントを削減し、消費電力を削減するラン・レングス符号化データによってゼロを利用する、新規の低電力データフローアーキテクチャである。 Eyerissの用語を使用すると、TPUの畳み込みレイヤは、CとMを行列単位の行と列にマッピングし、HWNサイクルで1回のパスを実行する。高いC / Mでは、レイヤを処理するためにRSパスが必要となる。低いC / Mでは、いくつかの技法がパスを減らし、使用率を向上させる。 (詳細はオンラインの参考文献[Ros15a] [Ros15b] [Ros15c] [Ros15f] [Tho15] [You15])にある。

Minervaはアルゴリズム、アーキテクチャ、回路分野を横断して、活性化データを小さな値でプルーニングし、部分的にデータを量子化することで、8倍の電力を削減する小システムである[Rea16]。

Eyerissは、入力がゼロのときの計算を避けることで、メモリのフットプリントを削減し、消費電力を削減するラン・レングス符号化データによってゼロを利用する、新規の低電力データフローアーキテクチャである。 Eyerissの用語を使用すると、TPUの畳み込みレイヤは、CとMを行列単位の行と列にマッピングし、HWNサイクルで1回のパスを実行する。高いC / Mでは、レイヤを処理するためにRSパスが必要となる。低いC / Mでは、いくつかの技法がパスを減らし、使用率を向上させる。 (詳細はオンラインの参考文献[Ros15a] [Ros15b] [Ros15c] [Ros15f] [Tho15] [You15])にある。

Minervaはアルゴリズム、アーキテクチャ、回路分野を横断して、活性化データを小さな値でプルーニングし、部分的にデータを量子化することで、8倍の電力を削減する小システムである[Rea16]。

[Gup15]は、推論ではなく、訓練のために16ビットの固定小数点演算を調べています。他のものは、計算中にアナログ回路を利用してエネルギーと性能を改善することにより、DNN計算の精度をより低くしている[LiK16] [Sha16]。命令セットをDNNに合わせることで、Cambriconはコードサイズを縮小する[Liu16]。最近の研究では、NNのためのプロセッサインメモリアーキテクチャ[Chi16] [Kim16]が注目された。

[Gup15] [Che14a] [Zha15]の3つのすべてが、計算中にDRAMにアクティベーションを格納する。 TPUのユニファイド・バッファは、通常の動作中にDRAMのスペリングやリロードが発生しないようなサイズになっている。

ルーフライン・パフォーマンス・モデルが示すように、TPUの使用を制限するメモリ帯域幅は比較的小さいI / Oバスであるにもかかわらず、6つのNNアプリケーションのうち4つはメモリにバインドされている。この結果は、Amdahlの法則「Cornucopia Corollary」を示唆している。すなわち、巨大で安価なリソースを使用することは、コスト効率の高いパフォーマンスを引き続き提供できるということだ。

TPUは、K80 GPUの32ビット浮動小数点データパス上の8ビット整数シストリック行列乗算器のエネルギーと面積の縮小を利用して、25倍のMACを詰め込み(65,536個 x 8ビット vs. 2,496個 x 32ビット )と3.5倍のオンチップメモリ(28 MiB vs. 8 MiB)で、比較的小さなダイにもかかわらずK80の消費電力の半分以下を使用する。この大きなメモリは、豊富なMACをさらに十分に活用できるように、アプリケーションの運用強度を向上させる。

我々は、最近、アーキテクチャコミュニティが、CNNに重点を置いていたにもかかわらず、データセンターの代表的なNNワークロードの約5%しか占めないことを発見した。これは、MLPおよびLSTMにもっと注意を払う必要があることを示している。

歴史は繰り返すというように、多くのシステム設計者が、浮動小数点パフォーマンスに集中していた時に、多くの主流のワークロードが整数操作によって支配されることが判明した時と似ている。

我々は、1秒当たりの推論(IPS)は、ベースのハードウェアの機能というより、NNの一つ機能に過ぎず、それは、NNプロセッサーのパフォーマンスのメトリックとしては、CPUとGPUにとってのMIPやMFLOPSIPSよりも、ずっと悪いことを確認した。

また、我々は、推論アプリケーションはユーザ対応のアプリケーションの一部であることが多いため、応答時間の制約が深刻であることを知った。このNNアーキテクチャが、うまく働く為には、99パーセンタイルを占めるこうしたアプリの待ち時間に対する厳しい制限に対応する必要がある。 K80は訓練では優れているかもしれないが、平均して、レイテンシよりもスループットに重点が置かれているため、平均してHaswellよりも少し早いだけである。これは、推論アプリケーションの厳しい応答時間の制限と衝突する。

TPUダイは、MACおよびオンチップメモリの利点を活用して、ドメイン固有のTensorFlowフレームワークを使用して書かれた短いプログラムを、K80 GPUのダイの15倍の速さで実行することで、29倍のパフォーマンス/ワットの利点をもたらす。それは、パフォーマンス/総所有コストと関連する。Haswell CPUダイと比べれば、前者は29倍、後者は83倍になる。

将来のCPUとGPUは確かに推論を高速に実行するだろうが、2015年頃のGPUメモリを使用して再設計されたTPUは、さらに2〜3倍高速になり、パフォーマンス/ワットの利点を高めることになる。 それは、K80の70倍近く、Haswellの200倍にもなる。

要約すると、次の要因で、TPUは成功した。

コンピュータアーキテクチャでは、商用製品間にとても大きな違いが生まれることはまれであり、TPUがドメイン固有アーキテクチャの原型になる可能性がある。我々は、多くの人がバーをさらに高くする後継機を育てることを期待している。

我々は、TPUの必要性を認識し、構築、配布、評価、公開するためのリソースを提供するためのGoogleのリーダーシップに感謝している。プロジェクトの開始を手伝ってくれたLuiz BarrosoとJames Laudonに感謝する。

TPUのようなシステムのハードウェアとソフトウェアを設計、検証、実装し、規模を拡大して製造、展開、使用するためには、「村」が必要となる。 この論文の著者が多いのは、その為である(2016年に加わったDavid Pattersonを除くすべての著者が、TPUのために働いた。)最初の4人の著者が、この記事の中の評価の大部分を行なった。 Jouppiはプロジェクト全体の上級アーキテクトでもあった。事務係としての彼の仕事の報酬として、彼は筆頭著者になった。

[Alb16] Albericio, J., Judd, P., Hetherington, T., Aamodt, T., Jerger, N.E. and Moshovos, A., 2016 Cnvlutin: Ineffectual-Neuron-Free Deep Neural Network Computing. Proceedings of the 43rd International Symposium on Computer Architecture.

[Ado16] Adolf, R., Rama, S., Reagen, B., Wei, G.Y. and Brooks, D., 2016, September. Fathom: reference workloads for modern deep learning methods.

IEEE International Symposium on Workload Characterization (IISWC).

[Asa02] Asanović, K. 2002. Programmable Neurocomputing, in The Handbook of Brain Theory and Neural Networks: Second Edition, M. A. Arbib (Ed.),

MIT Press, ISBN 0-262-01197-2, November 2002. https://people.eecs.berkeley.edu/~krste/papers/neurocomputing.pdf

[Asa98] Asanović, K. 1998. Asanović, K., Beck, Johnson, J., Wawrzynek, J., Kingsbury, B. and Morgan, N., November 1998. Training Neural Networks with Spert-II. Chapter 11 in Parallel Architectures for Artificial Networks: Paradigms and Implementations, N. Sundararajan and P. Saratchandran (Eds.),

IEEE Computer Society Press, ISBN 0-8186-8399-6. https://people.eecs.berkeley.edu/~krste/papers/annbook.pdf [Bar07] Barroso, L.A. and Hölzle, U., 2007. The case for energy-proportional computing. IEEE Computer, vol. 40. [Bar16] Barr, J. September 29, 2016, New P2 Instance Type for Amazon EC2 – Up to 16 GPUs. https://aws.amazon.com/blogs/aws/new-p2-instance-type-for-amazon-ec2-up-to-16-gpus/

[Bro16] Brooks, D. November 4, 2016. Private communication.

[Cau 16] Caulfield, A.M., Chung, E.S., Putnam, A., Haselman, H.A.J.F.M., Humphrey, S.H.M., Daniel, P.K.J.Y.K., Ovtcharov, L.T.M.K., Lanka,

M.P.L.W.S. and Burger, D.C.D., 2016. A Cloud-Scale Acceleration Architecture. MICRO conference.

[Cav15] Cavigelli, L., Gschwend, D., Mayer, C., Willi, S., Muheim, B. and Benini, L., 2015, May. Origami: A convolutional network accelerator.

Proceedings of the 25th edition on Great Lakes Symposium on VLSI.

[Cha10] Chakradhar, S., Sankaradas, M., Jakkula, V. and Cadambi, S., 2010, June. A dynamically configurable coprocessor for convolutional neural networks. Proceedings of the 37th International Symposium on Computer Architecture.

[Che14a] Chen, T., Du, Z., Sun, N., Wang, J., Wu, C., Chen, Y. and Temam, O., 2014. Diannao: A small-footprint high-throughput accelerator for ubiquitous machine-learning. Proceedings of ASPLOS.

[Che14b] Chen, Y., Luo, T., Liu, S., Zhang, S., He, L., Wang, J., Li, L., Chen, T., Xu, Z., Sun, N. and Temam, O., 2014, December. Dadiannao: A machine-learning supercomputer. Proceedings of the 47th Annual International Symposium on Microarchitecture.

[Che16a] Chen, Y.H., Emer, J. and Sze, V., 2016. Eyeriss: A Spatial Architecture for Energy-Efficient Dataflow for Convolutional Neural Networks.

Proceedings of the 43rd International Symposium on Computer Architecture.

[Che16b] Chen, Y., Chen, T.,Xu, Z., Sun, N., and Teman, O., 2016. DianNao Family: Energy-Efficient Hardware Accelerators for Machine Learning, Research Highlight, Communications of the ACM, 59(11).

[Chi16] Chi, P., Li, S., Qi, Z., Gu, P., Xu, C., Zhang, T., Zhao, J., Liu, Y., Wang, Y. and Xie, Y., 2016. PRIME: A Novel Processing-In-Memory Architecture for Neural Network Computation in ReRAM-based Main Memory. Proceedings of the 43rd International Symposium on Computer Architecture.

[Cla15] Clark, J. October 26, 2015, Google Turning Its Lucrative Web Search Over to AI Machines. Bloomberg Technology, www.bloomberg.com. [Dal16] Dally, W. February 9, 2016. High Performance Hardware for Machine Learning, Cadence ENN Summit.

[Dea13] Dean, J. and Barroso, L.A., 2013. The tail at scale. Communications of the ACM, 56(2).

[Dea16] Dean, J. July 7, 2016 Large-Scale Deep Learning with TensorFlow for Building Intelligent Systems, ACM Webinar.

[Du15] Du, Z., Fasthuber, R., Chen, T., Ienne, P., Li, L., Luo, T., Feng, X., Chen, Y. and Temam, O., 2015, June. ShiDianNao: shifting vision processing closer to the sensor. Proceedings of the 42nd International Symposium on Computer Architecture.

[Far09] Farabet, C., Poulet, C., Han, J.Y. and LeCun, Y., 2009, August. Cnp: An FPGA-based processor for convolutional networks. 2009 International Conference on Field Programmable Logic and Applications.

[Far11] Farabet, C., Martini, B., Corda, B., Akselrod, P., Culurciello, E. and LeCun, Y., 2011, June. Neuflow: A runtime reconfigurable dataflow processor for vision. In CVRP 2011 Workshops.

[Gup15] Gupta, S., Agrawal, A., Gopalakrishnan, K. and Narayanan, P., 2015, July. Deep Learning with Limited Numerical Precision. ICML.

[Ham90] Hammerstrom, D., 1990, June. A VLSI architecture for high-performance, low-cost, on-chip learning. 1990 IJCNN International Joint Conference on Neural Networks.

[Han15] Han, S.; Pool, J.; Tran, J.; and Dally, W., 2015. Learning both weights and connections for efficient neural networks. In Advances in Neural Information Processing Systems.

[Han16] Han, S., Liu, X., Mao, H., Pu, J., Pedram, A., Horowitz, M.A. and Dally, W.J., 2016. EIE: efficient inference engine on compressed deep neural network. Proceedings of the 43rd International Symposium on Computer Architecture.

[He16] He, K., Zhang, X., Ren, S. and Sun, J., 2016. Identity mappings in deep residual networks. Also in arXiv preprint arXiv:1603.05027. [Hen11] Hennessy, J.L. and Patterson, D.A., 2018. Computer architecture: a quantitative approach, 6th edition, Elsevier.

[Höl09] Hölzle, U. and Barroso, L., 2009. The datacenter as a computer. Morgan and Claypool.

[Ien96] Ienne, P., Cornu, T. and Kuhn, G., 1996. Special-purpose digital hardware for neural networks: An architectural survey. Journal of VLSI signal processing systems for signal, image and video technology, 13(1).

[Int16] Intel, 2016, Intel® Xeon® Processor E5-4669 v3, http://ark.intel.com/products/85766/Intel-Xeon-Processor-E5-4669-v3-45M-Cache-2_10-GHz [Jou16] Jouppi, N. May 18, 2016. Google supercharges machine learning tasks with TPU custom chip. https://cloudplatform.googleblog.com

[Keu16] Keutzer, K., 2016. If I could only design one circuit…: technical perspective. Communications of the ACM, 59(11),.

[Kim16] Kim, D., Kung, J.H., Chai, S., Yalamanchili, S. and Mukhopadhyay, S., 2016. Neurocube: A Programmable Digital Neuromorphic Architecture with High-Density 3D Memory. Proceedings of the 43rd International Symposium on Computer Architecture.

[Kri12] Krizhevsky, A., Sutskever, I. and Hinton, G., 2012. Imagenet classification with deep convolutional neural networks. Advances in neural information processing systems.

[Kun80] Kung, H.T. and Leiserson, C.E., 1980. Algorithms for VLSI processor arrays. Introduction to VLSI systems. [Lan09] Lange, K.D., 2009. Identifying shades of green: The SPECpower benchmarks. IEEE Computer, 42(3).

[Lar16] Larabel, M. March 10, 2016, Google Looks To Open Up StreamExecutor To Make GPGPU Programming Easier, Phoronix, https://www.phoronix.com/scan.php?page=news_item&px=Google-StreamExec-Parallel.

[LiK16] LiKamWa, R., Hou, Y., Gao, J., Polansky, M. and Zhong, L., 2016. RedEye: Analog ConvNet Image Sensor Architecture for Continuous Mobile Vision. Proceedings of the 43rd International Symposium on Computer Architecture.

[Liu15] Liu, D., Chen, T., Liu, S., Zhou, J., Zhou, S., Teman, O., Feng, X., Zhou, X. and Chen, Y., 2015, March. Pudiannao: A polyvalent machine learning accelerator. Proceedings of the 42nd International Symposium on Computer Architecture.

[Liu16] Liu, S., Du, Z.D., Tao, J.H., Han, D., Luo, T., Xie, Y., Chen, Y. and Chen, T., 2016. Cambricon: An instruction set architecture for neural networks. Proceedings of the 43rd International Symposium on Computer Architecture.

[Met16] Metz, C. September 26, 2016, Microsoft Bets Its Future On A Reprogrammable Computer Chip, Wired Magazine, https://www.wired.com/2016/09/microsoft-bets-future-chip-reprogram-fly/

[Nvi15] Nvidia, January 2015. Tesla K80 GPU Accelerator. Board Specification https://images.nvidia.com/content/pdf/kepler/Tesla-K80-BoardSpec-07317-001-v05.pdf.

[Nvi16] Nvidia, 2016. Tesla GPU Accelerators For Servers. http://www.nvidia.com/object/tesla-servers.html.

[Ovt15a] Ovtcharov, K., Ruwase, O., Kim, J.Y., Fowers, J., Strauss, K. and Chung, E.S., February 2, 2015. Accelerating deep convolutional neural networks using specialized hardware. Microsoft Research Whitepaper.

https://www.microsoft.com/en-us/research/publication/accelerating-deep-convolutional-neural-networks-using-specialized-hardware/

[Ovt15b] Ovtcharov, K., Ruwase, O., Kim, J.Y., Fowers, J., Strauss, K. and Chung, E.S., 2015, August. Toward accelerating deep learning at scale using specialized hardware in the datacenter. 2015 IEEE Hot Chips 27 Symposium.

[Pat04] Patterson, D.A., 2004. Latency lags bandwith. Communications of the ACM, 47(10).

[Pee13] Peemen, M., Setio, A.A., Mesman, B. and Corporaal, H., 2013, October. Memory-centric accelerator design for convolutional neural networks. In

2013 IEEE 31st International Conference on Computer Design (ICCD).

[Put14] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2014, June. A reconfigurable fabric for accelerating large-scale datacenter services. 41st International Symposium on Computer Architecture.

[Put15] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2015. A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services. IEEE Micro, 35(3).

[Put16] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2016. A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services. Communications of the ACM.

[Qad13] Qadeer, W., Hameed, R., Shacham, O., Venkatesan, P., Kozyrakis, C. and Horowitz, M.A., 2013, June. Convolution engine: balancing efficiency & flexibility in specialized computing. Proceedings of the 40th International Symposium on Computer Architecture.

[Ram91] Ramacher, U., Beichter, J., Raab, W., Anlauf, J., Bruels, N., Hachmann, U. and Wesseling, M., 1991. Design of a 1st Generation Neurocomputer. In VLSI design of Neural Networks. Springer US.

[Rea16] Reagen, B., Whatmough, P., Adolf, R., Rama, S., Lee, H., Lee, S.K., Hernández-Lobato, J.M., Wei, G.Y. and Brooks, D., 2016. Minerva: Enabling low-power, highly-accurate deep neural network accelerators. Proceedings of the 43rd International Symposium on Computer Architecture. [Ros15a] Ross, J., Jouppi, N., Phelps, A., Young, C., Norrie, T., Thorson, G., Luu, D., 2015. Neural Network Processor, Patent Application No. 62/164,931. [Ros15b] Ross, J., Phelps, A., 2015. Computing Convolutions Using a Neural Network Processor, , Patent Application No. 62/164,902.

[Ros15c] Ross, J., 2015. Prefetching Weights for a Neural Network Processor, Patent Application No. 62/164,981. [Ros15d] Ross, J., Thorson, G., 2015. Rotating Data for Neural Network Computations,Patent Application No. 62/164,908.

[Rus15] Russakovsky, O., Deng, J., Su, H., Krause, J., Satheesh, S., Ma, S., Huang, Z., Karpathy, A., Khosla, A., Bernstein, M. and Berg, A.C., 2015. Imagenet large scale visual recognition challenge. International Journal of Computer Vision, 115(3).

[Sch09] Schurman, E. and Brutlag, J., 2009, June. The user and business impact of server delays, additional bytes, and HTTP chunking in web search. In

Velocity Web Performance and Operations Conference.

[Sha16] Shafiee, A., Nag, A., Muralimanohar, N., Balasubramonian, R., Strachan, J.P., Hu, M., Williams, R.S. and Srikumar, V., 2016. ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars. Proceedings of the 43rd International Symposium on Computer Architecture.

[Sil16] Silver, D., Huang, A., Maddison, C.J., Guez, A., Sifre, L., Van Den Driessche, G., Schrittwieser, J., Antonoglou, I., Panneershelvam, V., Lanctot,

M. and Dieleman, S., 2016. Mastering the game of Go with deep neural networks and tree search. Nature, 529(7587).

[Smi82] Smith, J.E., 1982, April. Decoupled access/execute computer architectures. Proceedings of the 11th International Symposium on Computer Architecture.

[Ste15] Steinberg, D., 2015. Full-Chip Simulations, Keys to Success. Proceedings of the Synopsys Users Group (SNUG) Silicon Valley 2015. [Sze15] Szegedy, C., Liu, W., Jia, Y., Sermanet, P., Reed, S., Anguelov, D., Erhan, D., Vanhoucke, V. and Rabinovich, A., 2015. Going deeper with convolutions. Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition.

[Tho15] Thorson, G., Clark, C., Luu, D., 2015. Vector Computation Unit in a Neural Network Processor, Patent Application No. 62/165,022. [Wil09] Williams, S., Waterman, A. and Patterson, D., 2009. Roofline: an insightful visual performance model for multicore architectures. Communications of the ACM.

[Wu16] Wu, Y., Schuster, M., Chen, Z., Le, Q., Norouzi, M., Macherey, W., Krikun, M., Cao, Y., Gao, Q., Macherey, K., Klingner, J., Shah, A., Johnson,

M., Liu, X., Kaiser, Ł., Gouws, S., Kato, Y., Kudo, T., Kazawa, H., Stevens, K., Kurian, G., Patil, N., Wang, W., Young, C., Smith, J., Riesa, J., Rudnick, A., Vinyals, O., Corrado, G., Hughes, M., and Dean, J. September 26, 2016, Google's Neural Machine Translation System: Bridging the Gap between Human and Machine Translation, http://arxiv.org/abs/1609.08144.

[You15] Young, C., 2015. Batch Processing in a Neural Network Processor, Patent Application No. 62/165,020.

[Zha15] Zhang, C., Li, P., Sun, G., Guan, Y., Xiao, B. and Cong, J., 2015, February. Optimizing FPGA-based accelerator design for deep convolutional neural networks. Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays.

TPUをこれらのアーキテクチャーと比較する

- [Che14a]は、DRAMから入力バッファとウェイトバッファにデータをDMAする。これらは、乗算、加算、および非線形関数を実行する3ステージパイプラインNFUによって読み取られる。結果は出力バッファに送られ、次にDRAMに送られる。 NFUは記憶装置を持たず、シストリックではない。

- [Gup15]は、シストリックアレイに部分和を格納しながら、両方の行列入力をストリーミングするように見える。 TPUは重み行列のタイルを記憶している間に、他方の入力および活動化前の部分和をストリーミングする。 TPUは確率的丸めをサポートしていない。

- [Zha15]は、TPUマトリックスユニットの4x2バージョンに相当する計算ユニットから構築されている。 ASICでは、入力バッファと出力バッファをこれらの計算エンジンに接続するクロスバーの配線コストが重要になる。我々は[Zha15]の計算エンジンの結果を組み合わせるための追加的な削減のためのアーキテクチャサポートを見ていないことに驚いている。

[Gup15] [Che14a] [Zha15]の3つのすべてが、計算中にDRAMにアクティベーションを格納する。 TPUのユニファイド・バッファは、通常の動作中にDRAMのスペリングやリロードが発生しないようなサイズになっている。

10. 結論

ルーフライン・パフォーマンス・モデルが示すように、TPUの使用を制限するメモリ帯域幅は比較的小さいI / Oバスであるにもかかわらず、6つのNNアプリケーションのうち4つはメモリにバインドされている。この結果は、Amdahlの法則「Cornucopia Corollary」を示唆している。すなわち、巨大で安価なリソースを使用することは、コスト効率の高いパフォーマンスを引き続き提供できるということだ。

TPUは、K80 GPUの32ビット浮動小数点データパス上の8ビット整数シストリック行列乗算器のエネルギーと面積の縮小を利用して、25倍のMACを詰め込み(65,536個 x 8ビット vs. 2,496個 x 32ビット )と3.5倍のオンチップメモリ(28 MiB vs. 8 MiB)で、比較的小さなダイにもかかわらずK80の消費電力の半分以下を使用する。この大きなメモリは、豊富なMACをさらに十分に活用できるように、アプリケーションの運用強度を向上させる。

我々は、最近、アーキテクチャコミュニティが、CNNに重点を置いていたにもかかわらず、データセンターの代表的なNNワークロードの約5%しか占めないことを発見した。これは、MLPおよびLSTMにもっと注意を払う必要があることを示している。

歴史は繰り返すというように、多くのシステム設計者が、浮動小数点パフォーマンスに集中していた時に、多くの主流のワークロードが整数操作によって支配されることが判明した時と似ている。

我々は、1秒当たりの推論(IPS)は、ベースのハードウェアの機能というより、NNの一つ機能に過ぎず、それは、NNプロセッサーのパフォーマンスのメトリックとしては、CPUとGPUにとってのMIPやMFLOPSIPSよりも、ずっと悪いことを確認した。

また、我々は、推論アプリケーションはユーザ対応のアプリケーションの一部であることが多いため、応答時間の制約が深刻であることを知った。このNNアーキテクチャが、うまく働く為には、99パーセンタイルを占めるこうしたアプリの待ち時間に対する厳しい制限に対応する必要がある。 K80は訓練では優れているかもしれないが、平均して、レイテンシよりもスループットに重点が置かれているため、平均してHaswellよりも少し早いだけである。これは、推論アプリケーションの厳しい応答時間の制限と衝突する。

TPUダイは、MACおよびオンチップメモリの利点を活用して、ドメイン固有のTensorFlowフレームワークを使用して書かれた短いプログラムを、K80 GPUのダイの15倍の速さで実行することで、29倍のパフォーマンス/ワットの利点をもたらす。それは、パフォーマンス/総所有コストと関連する。Haswell CPUダイと比べれば、前者は29倍、後者は83倍になる。

将来のCPUとGPUは確かに推論を高速に実行するだろうが、2015年頃のGPUメモリを使用して再設計されたTPUは、さらに2〜3倍高速になり、パフォーマンス/ワットの利点を高めることになる。 それは、K80の70倍近く、Haswellの200倍にもなる。

要約すると、次の要因で、TPUは成功した。

- 大型の -- そんなには大型ではないのだが -- 行列乗算ユニット。

- 実質的なソフトウェア制御のオンチップメモリ。

- ホストCPUへの依存を減らす、全推論モデルを実行する能力。

- 99パーセンタイルの応答時間制限によく一致することが判明したシングルスレッドの決定論的実行モデル。

- 2017年のNNと2013年のNNをマッチさせる十分な柔軟性。

- 大規模なデータパスとメモリにもかかわらず、小型で低消費電力のダイを可能にした汎用機能の省略。

- 量子化されたアプリケーションによる8ビット整数の使用。

- アプリケーションはTensorFlowを使用して書かれているため、異なるTPUハードウェアでうまく動作するように書き直すのではなく、高性能でTPUに簡単に移植することができる。

コンピュータアーキテクチャでは、商用製品間にとても大きな違いが生まれることはまれであり、TPUがドメイン固有アーキテクチャの原型になる可能性がある。我々は、多くの人がバーをさらに高くする後継機を育てることを期待している。

謝辞

我々は、TPUの必要性を認識し、構築、配布、評価、公開するためのリソースを提供するためのGoogleのリーダーシップに感謝している。プロジェクトの開始を手伝ってくれたLuiz BarrosoとJames Laudonに感謝する。

TPUのようなシステムのハードウェアとソフトウェアを設計、検証、実装し、規模を拡大して製造、展開、使用するためには、「村」が必要となる。 この論文の著者が多いのは、その為である(2016年に加わったDavid Pattersonを除くすべての著者が、TPUのために働いた。)最初の4人の著者が、この記事の中の評価の大部分を行なった。 Jouppiはプロジェクト全体の上級アーキテクトでもあった。事務係としての彼の仕事の報酬として、彼は筆頭著者になった。

参考文献

[Aba16] Abadi, M., Agarwal, A., Barham, P., Brevdo, E., Chen, Z., Citro, C., Corrado, G.S., Davis, A., Dean, J., Devin, M. and Ghemawat, S., 2016. Tensorflow: Large-scale machine learning on heterogeneous distributed systems. arXiv preprint arXiv:1603.04467.[Alb16] Albericio, J., Judd, P., Hetherington, T., Aamodt, T., Jerger, N.E. and Moshovos, A., 2016 Cnvlutin: Ineffectual-Neuron-Free Deep Neural Network Computing. Proceedings of the 43rd International Symposium on Computer Architecture.

[Ado16] Adolf, R., Rama, S., Reagen, B., Wei, G.Y. and Brooks, D., 2016, September. Fathom: reference workloads for modern deep learning methods.

IEEE International Symposium on Workload Characterization (IISWC).

[Asa02] Asanović, K. 2002. Programmable Neurocomputing, in The Handbook of Brain Theory and Neural Networks: Second Edition, M. A. Arbib (Ed.),

MIT Press, ISBN 0-262-01197-2, November 2002. https://people.eecs.berkeley.edu/~krste/papers/neurocomputing.pdf

[Asa98] Asanović, K. 1998. Asanović, K., Beck, Johnson, J., Wawrzynek, J., Kingsbury, B. and Morgan, N., November 1998. Training Neural Networks with Spert-II. Chapter 11 in Parallel Architectures for Artificial Networks: Paradigms and Implementations, N. Sundararajan and P. Saratchandran (Eds.),

IEEE Computer Society Press, ISBN 0-8186-8399-6. https://people.eecs.berkeley.edu/~krste/papers/annbook.pdf [Bar07] Barroso, L.A. and Hölzle, U., 2007. The case for energy-proportional computing. IEEE Computer, vol. 40. [Bar16] Barr, J. September 29, 2016, New P2 Instance Type for Amazon EC2 – Up to 16 GPUs. https://aws.amazon.com/blogs/aws/new-p2-instance-type-for-amazon-ec2-up-to-16-gpus/

[Bro16] Brooks, D. November 4, 2016. Private communication.

[Cau 16] Caulfield, A.M., Chung, E.S., Putnam, A., Haselman, H.A.J.F.M., Humphrey, S.H.M., Daniel, P.K.J.Y.K., Ovtcharov, L.T.M.K., Lanka,

M.P.L.W.S. and Burger, D.C.D., 2016. A Cloud-Scale Acceleration Architecture. MICRO conference.

[Cav15] Cavigelli, L., Gschwend, D., Mayer, C., Willi, S., Muheim, B. and Benini, L., 2015, May. Origami: A convolutional network accelerator.

Proceedings of the 25th edition on Great Lakes Symposium on VLSI.

[Cha10] Chakradhar, S., Sankaradas, M., Jakkula, V. and Cadambi, S., 2010, June. A dynamically configurable coprocessor for convolutional neural networks. Proceedings of the 37th International Symposium on Computer Architecture.

[Che14a] Chen, T., Du, Z., Sun, N., Wang, J., Wu, C., Chen, Y. and Temam, O., 2014. Diannao: A small-footprint high-throughput accelerator for ubiquitous machine-learning. Proceedings of ASPLOS.

[Che14b] Chen, Y., Luo, T., Liu, S., Zhang, S., He, L., Wang, J., Li, L., Chen, T., Xu, Z., Sun, N. and Temam, O., 2014, December. Dadiannao: A machine-learning supercomputer. Proceedings of the 47th Annual International Symposium on Microarchitecture.

[Che16a] Chen, Y.H., Emer, J. and Sze, V., 2016. Eyeriss: A Spatial Architecture for Energy-Efficient Dataflow for Convolutional Neural Networks.

Proceedings of the 43rd International Symposium on Computer Architecture.

[Che16b] Chen, Y., Chen, T.,Xu, Z., Sun, N., and Teman, O., 2016. DianNao Family: Energy-Efficient Hardware Accelerators for Machine Learning, Research Highlight, Communications of the ACM, 59(11).

[Chi16] Chi, P., Li, S., Qi, Z., Gu, P., Xu, C., Zhang, T., Zhao, J., Liu, Y., Wang, Y. and Xie, Y., 2016. PRIME: A Novel Processing-In-Memory Architecture for Neural Network Computation in ReRAM-based Main Memory. Proceedings of the 43rd International Symposium on Computer Architecture.

[Cla15] Clark, J. October 26, 2015, Google Turning Its Lucrative Web Search Over to AI Machines. Bloomberg Technology, www.bloomberg.com. [Dal16] Dally, W. February 9, 2016. High Performance Hardware for Machine Learning, Cadence ENN Summit.

[Dea13] Dean, J. and Barroso, L.A., 2013. The tail at scale. Communications of the ACM, 56(2).

[Dea16] Dean, J. July 7, 2016 Large-Scale Deep Learning with TensorFlow for Building Intelligent Systems, ACM Webinar.

[Du15] Du, Z., Fasthuber, R., Chen, T., Ienne, P., Li, L., Luo, T., Feng, X., Chen, Y. and Temam, O., 2015, June. ShiDianNao: shifting vision processing closer to the sensor. Proceedings of the 42nd International Symposium on Computer Architecture.

[Far09] Farabet, C., Poulet, C., Han, J.Y. and LeCun, Y., 2009, August. Cnp: An FPGA-based processor for convolutional networks. 2009 International Conference on Field Programmable Logic and Applications.

[Far11] Farabet, C., Martini, B., Corda, B., Akselrod, P., Culurciello, E. and LeCun, Y., 2011, June. Neuflow: A runtime reconfigurable dataflow processor for vision. In CVRP 2011 Workshops.

[Gup15] Gupta, S., Agrawal, A., Gopalakrishnan, K. and Narayanan, P., 2015, July. Deep Learning with Limited Numerical Precision. ICML.

[Ham90] Hammerstrom, D., 1990, June. A VLSI architecture for high-performance, low-cost, on-chip learning. 1990 IJCNN International Joint Conference on Neural Networks.

[Han15] Han, S.; Pool, J.; Tran, J.; and Dally, W., 2015. Learning both weights and connections for efficient neural networks. In Advances in Neural Information Processing Systems.

[Han16] Han, S., Liu, X., Mao, H., Pu, J., Pedram, A., Horowitz, M.A. and Dally, W.J., 2016. EIE: efficient inference engine on compressed deep neural network. Proceedings of the 43rd International Symposium on Computer Architecture.

[He16] He, K., Zhang, X., Ren, S. and Sun, J., 2016. Identity mappings in deep residual networks. Also in arXiv preprint arXiv:1603.05027. [Hen11] Hennessy, J.L. and Patterson, D.A., 2018. Computer architecture: a quantitative approach, 6th edition, Elsevier.

[Höl09] Hölzle, U. and Barroso, L., 2009. The datacenter as a computer. Morgan and Claypool.

[Ien96] Ienne, P., Cornu, T. and Kuhn, G., 1996. Special-purpose digital hardware for neural networks: An architectural survey. Journal of VLSI signal processing systems for signal, image and video technology, 13(1).

[Int16] Intel, 2016, Intel® Xeon® Processor E5-4669 v3, http://ark.intel.com/products/85766/Intel-Xeon-Processor-E5-4669-v3-45M-Cache-2_10-GHz [Jou16] Jouppi, N. May 18, 2016. Google supercharges machine learning tasks with TPU custom chip. https://cloudplatform.googleblog.com

[Keu16] Keutzer, K., 2016. If I could only design one circuit…: technical perspective. Communications of the ACM, 59(11),.

[Kim16] Kim, D., Kung, J.H., Chai, S., Yalamanchili, S. and Mukhopadhyay, S., 2016. Neurocube: A Programmable Digital Neuromorphic Architecture with High-Density 3D Memory. Proceedings of the 43rd International Symposium on Computer Architecture.

[Kri12] Krizhevsky, A., Sutskever, I. and Hinton, G., 2012. Imagenet classification with deep convolutional neural networks. Advances in neural information processing systems.

[Kun80] Kung, H.T. and Leiserson, C.E., 1980. Algorithms for VLSI processor arrays. Introduction to VLSI systems. [Lan09] Lange, K.D., 2009. Identifying shades of green: The SPECpower benchmarks. IEEE Computer, 42(3).

[Lar16] Larabel, M. March 10, 2016, Google Looks To Open Up StreamExecutor To Make GPGPU Programming Easier, Phoronix, https://www.phoronix.com/scan.php?page=news_item&px=Google-StreamExec-Parallel.

[LiK16] LiKamWa, R., Hou, Y., Gao, J., Polansky, M. and Zhong, L., 2016. RedEye: Analog ConvNet Image Sensor Architecture for Continuous Mobile Vision. Proceedings of the 43rd International Symposium on Computer Architecture.

[Liu15] Liu, D., Chen, T., Liu, S., Zhou, J., Zhou, S., Teman, O., Feng, X., Zhou, X. and Chen, Y., 2015, March. Pudiannao: A polyvalent machine learning accelerator. Proceedings of the 42nd International Symposium on Computer Architecture.

[Liu16] Liu, S., Du, Z.D., Tao, J.H., Han, D., Luo, T., Xie, Y., Chen, Y. and Chen, T., 2016. Cambricon: An instruction set architecture for neural networks. Proceedings of the 43rd International Symposium on Computer Architecture.

[Met16] Metz, C. September 26, 2016, Microsoft Bets Its Future On A Reprogrammable Computer Chip, Wired Magazine, https://www.wired.com/2016/09/microsoft-bets-future-chip-reprogram-fly/

[Nvi15] Nvidia, January 2015. Tesla K80 GPU Accelerator. Board Specification https://images.nvidia.com/content/pdf/kepler/Tesla-K80-BoardSpec-07317-001-v05.pdf.

[Nvi16] Nvidia, 2016. Tesla GPU Accelerators For Servers. http://www.nvidia.com/object/tesla-servers.html.

[Ovt15a] Ovtcharov, K., Ruwase, O., Kim, J.Y., Fowers, J., Strauss, K. and Chung, E.S., February 2, 2015. Accelerating deep convolutional neural networks using specialized hardware. Microsoft Research Whitepaper.

https://www.microsoft.com/en-us/research/publication/accelerating-deep-convolutional-neural-networks-using-specialized-hardware/

[Ovt15b] Ovtcharov, K., Ruwase, O., Kim, J.Y., Fowers, J., Strauss, K. and Chung, E.S., 2015, August. Toward accelerating deep learning at scale using specialized hardware in the datacenter. 2015 IEEE Hot Chips 27 Symposium.

[Pat04] Patterson, D.A., 2004. Latency lags bandwith. Communications of the ACM, 47(10).

[Pee13] Peemen, M., Setio, A.A., Mesman, B. and Corporaal, H., 2013, October. Memory-centric accelerator design for convolutional neural networks. In

2013 IEEE 31st International Conference on Computer Design (ICCD).

[Put14] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2014, June. A reconfigurable fabric for accelerating large-scale datacenter services. 41st International Symposium on Computer Architecture.

[Put15] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2015. A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services. IEEE Micro, 35(3).

[Put16] Putnam, A., Caulfield, A.M., Chung, E.S., Chiou, D., Constantinides, K., Demme, J., Esmaeilzadeh, H., Fowers, J., Gopal, G.P., Gray, J., Haselman, M., Hauck, S., Heil, S., Hormati, A., Kim, J-Y., Lanka, S., Larus, J., Peterson, E., Pope, S ., Smith, A., Thong, J., Xiao, P.Y., Burger, D. 2016. A Reconfigurable Fabric for Accelerating Large-Scale Datacenter Services. Communications of the ACM.

[Qad13] Qadeer, W., Hameed, R., Shacham, O., Venkatesan, P., Kozyrakis, C. and Horowitz, M.A., 2013, June. Convolution engine: balancing efficiency & flexibility in specialized computing. Proceedings of the 40th International Symposium on Computer Architecture.

[Ram91] Ramacher, U., Beichter, J., Raab, W., Anlauf, J., Bruels, N., Hachmann, U. and Wesseling, M., 1991. Design of a 1st Generation Neurocomputer. In VLSI design of Neural Networks. Springer US.

[Rea16] Reagen, B., Whatmough, P., Adolf, R., Rama, S., Lee, H., Lee, S.K., Hernández-Lobato, J.M., Wei, G.Y. and Brooks, D., 2016. Minerva: Enabling low-power, highly-accurate deep neural network accelerators. Proceedings of the 43rd International Symposium on Computer Architecture. [Ros15a] Ross, J., Jouppi, N., Phelps, A., Young, C., Norrie, T., Thorson, G., Luu, D., 2015. Neural Network Processor, Patent Application No. 62/164,931. [Ros15b] Ross, J., Phelps, A., 2015. Computing Convolutions Using a Neural Network Processor, , Patent Application No. 62/164,902.

[Ros15c] Ross, J., 2015. Prefetching Weights for a Neural Network Processor, Patent Application No. 62/164,981. [Ros15d] Ross, J., Thorson, G., 2015. Rotating Data for Neural Network Computations,Patent Application No. 62/164,908.

[Rus15] Russakovsky, O., Deng, J., Su, H., Krause, J., Satheesh, S., Ma, S., Huang, Z., Karpathy, A., Khosla, A., Bernstein, M. and Berg, A.C., 2015. Imagenet large scale visual recognition challenge. International Journal of Computer Vision, 115(3).

[Sch09] Schurman, E. and Brutlag, J., 2009, June. The user and business impact of server delays, additional bytes, and HTTP chunking in web search. In

Velocity Web Performance and Operations Conference.

[Sha16] Shafiee, A., Nag, A., Muralimanohar, N., Balasubramonian, R., Strachan, J.P., Hu, M., Williams, R.S. and Srikumar, V., 2016. ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars. Proceedings of the 43rd International Symposium on Computer Architecture.

[Sil16] Silver, D., Huang, A., Maddison, C.J., Guez, A., Sifre, L., Van Den Driessche, G., Schrittwieser, J., Antonoglou, I., Panneershelvam, V., Lanctot,

M. and Dieleman, S., 2016. Mastering the game of Go with deep neural networks and tree search. Nature, 529(7587).

[Smi82] Smith, J.E., 1982, April. Decoupled access/execute computer architectures. Proceedings of the 11th International Symposium on Computer Architecture.

[Ste15] Steinberg, D., 2015. Full-Chip Simulations, Keys to Success. Proceedings of the Synopsys Users Group (SNUG) Silicon Valley 2015. [Sze15] Szegedy, C., Liu, W., Jia, Y., Sermanet, P., Reed, S., Anguelov, D., Erhan, D., Vanhoucke, V. and Rabinovich, A., 2015. Going deeper with convolutions. Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition.

[Tho15] Thorson, G., Clark, C., Luu, D., 2015. Vector Computation Unit in a Neural Network Processor, Patent Application No. 62/165,022. [Wil09] Williams, S., Waterman, A. and Patterson, D., 2009. Roofline: an insightful visual performance model for multicore architectures. Communications of the ACM.

[Wu16] Wu, Y., Schuster, M., Chen, Z., Le, Q., Norouzi, M., Macherey, W., Krikun, M., Cao, Y., Gao, Q., Macherey, K., Klingner, J., Shah, A., Johnson,

M., Liu, X., Kaiser, Ł., Gouws, S., Kato, Y., Kudo, T., Kazawa, H., Stevens, K., Kurian, G., Patil, N., Wang, W., Young, C., Smith, J., Riesa, J., Rudnick, A., Vinyals, O., Corrado, G., Hughes, M., and Dean, J. September 26, 2016, Google's Neural Machine Translation System: Bridging the Gap between Human and Machine Translation, http://arxiv.org/abs/1609.08144.

[You15] Young, C., 2015. Batch Processing in a Neural Network Processor, Patent Application No. 62/165,020.

[Zha15] Zhang, C., Li, P., Sun, G., Guan, Y., Xiao, B. and Cong, J., 2015, February. Optimizing FPGA-based accelerator design for deep convolutional neural networks. Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays.

コメント

コメントを投稿